TTLとCMOSの安定したインターフェース回路

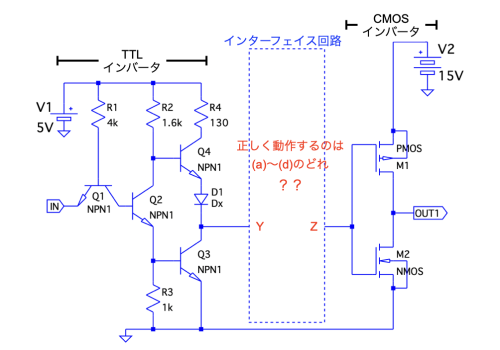

図1は,5V電源で動作するスタンダードTTLのインバータから,15Vで動作するCMOSのインバータへディジタル信号を伝えます.安定した信号を伝えるには波線で囲った箇所にインターフェース回路が必要となります.安定した信号を伝えるインターフェース回路は図2の(a)~(d)のどの回路でしょうか.

TTLの電源は5V,CMOSの電源は15V場合.

入力がYで出力がZ

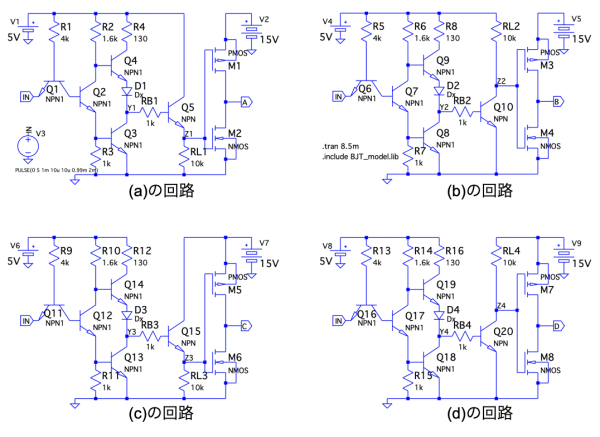

(a)の回路 (b)の回路 (c)の回路 (d)の回路

安定したディジタル信号を伝えるには,5Vで動くTTLのHigh("H")とLow("L")の出力レベルを,15Vで動くCMOSロジックの"H"と"L"の入力レベルに変換するインターフェースが必要になります.

CMOSのおおよその入力レベルは,"H"とみなす最小の入力電圧が2/3*VDD,"L"とみなす最大の入力電圧が1/3*VDDです.図1へ図2の(a)~(d)のインターフェース回路を入れて,CMOSロジックの入力レベルを満足する回路を検討すると分かります.

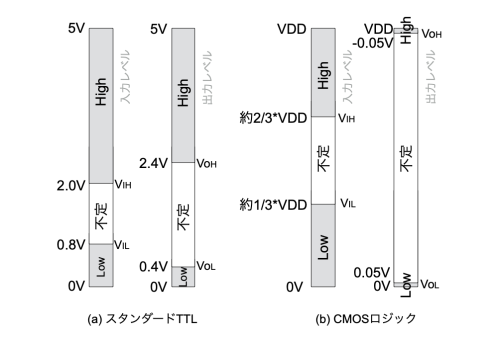

TTLとCMOSロジックは,図3のような入出力レベルになります.図1の場合は,TTLからCMOSへ信号を伝える回路なので,図3(a)のTTLの出力レベルをインターフェースで変換して,図3(b)のCMOSロジックの入力レベルに合わせます.図1では,CMOS側の電源は15Vなので,CMOSインバータが動作する要件は,"H"の入力レベルが「VIH≥10V」,"L"の入力レベルが「VIL≤5V」になり,この要件を満たす回路を図2の(a)~(d)から探すことになります.

(a)電源が5VのスタンダードTTL (b)電源が3~18VのCMOSロジック

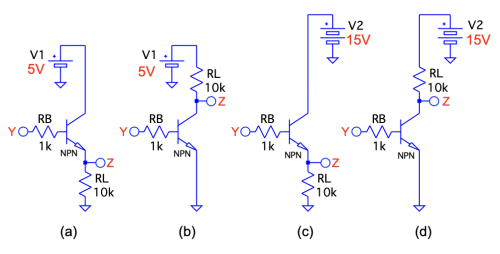

図2(a)は,電源が5Vのエミッタ・ホロワ回路です.エミッタ・ホロワ回路の出力電圧は,ベース電圧から決まります.具体的には,YにTTLの"H"レベルの5Vが加わると,おおよそのZの"H"レベルは,Yの電圧からトランジスタのベース・エミッタ間電圧(0.7V)を減じた4.3Vの電圧となります.Zの電圧はCMOSインバータの入力電圧ですので,「VIH=4.3V」になります.一方,YにTTLの"L"レベルの0Vが加わると,トランジスタは動かないので,Zの"L"レベルは0VとなりCMOSインバータの入力電圧は「VIL=0V」となります.この2つの入力レベルとCMOSインバータが動作する要件を比較すると,"H"側の要件を満たしません.よってCMOSインバータに信号が伝わらないので間違いです.

図2(b)は,電源が5Vのエミッタ接地回路です.エミッタ接地回路はYとZの信号が反転するインバータ回路になります.具体的には,Yに"H"レベルの5Vが加わるとトランジスタがONして,Zの"L"レベルはおおよそ0Vになり「VIL=0V」になります.一方,Yに"L"レベルの0Vが加わると,トランジスタがOFFして,Zの"H"レベルは5Vになり「VIH=5V」になります.この2つの入力レベルとCMOSインバータが動作する要件を比較すると,"H"側の要件を満たしません.よってCMOSインバータに信号が伝わらないので間違いです.

図2(c)は,電源が15Vのエミッタ・ホロワ回路です.図2(a)の検討と同じように,YにTTLの"H"レベルの5Vが加わると,おおよそのZの"H"レベルは,Yの電圧からトランジスタのベース・エミッタ間電圧(0.7V)を減じた4.3Vの電圧となります.Zの電圧はCMOSインバータの入力電圧ですので,「VIH=4.3V」になります.一方,YにTTLの"L"レベルの0Vが加わると,トランジスタは動かないので,Zの"L"レベルは0VとなりCMOSインバータの入力電圧は「VIL=0V」となります.この2つの入力レベルとCMOSインバータが動作する要件を比較すると,"H"側の要件を満たしません.よってCMOSインバータに信号が伝わらないので間違いです.

図2(d)は,電源が15Vのエミッタ接地回路です.図2(b)の検討と同じように,エミッタ接地回路はYとZが反転するインバータになります.Yに"H"レベルの5Vが加わると,トランジスタがONして,Zの"L"レベルはおおよそ0Vになり「VIL=0V」になります.Yに"L"レベルの0Vが加わると,トランジスタがOFFして,Zの"H"レベルは15Vになり「VIH=15V」になります.この2つの入力レベルはCMOSインバータが動作する要件を満たすので,図2(d)が正解になります.

●TTLとCMOSのインターフェースについて

TTLとCMOSロジックは,よく使われるロジック・ファミリで,TTLは5Vで動作し,CMOSロジックは3V~18Vの広い電源電圧範囲で動作します.同じファミリ内であれば論理ゲートを直に接続できます.しかし,異なるロジック・ファミリ間ではインターフェース回路が必要になります.インターフェース回路は,前段の出力レベルを後段の入力レベルになるように電圧レベルを変換します.そしてその電圧レベルを保つ電流能力を備えた回路になります.以下は,TTLからCMOSへのインターフェースと,CMOSからTTLへのインターフェースについて解説します.

●異なる電源で動作するTTLからCMOSへのインターフェース(その1)

異なる電源で動作するTTLからCMOSへのインターフェースの1つ目の方法が,図1に図2(d)を入れた回路になります.まず初めに図1の答え合わせをします.

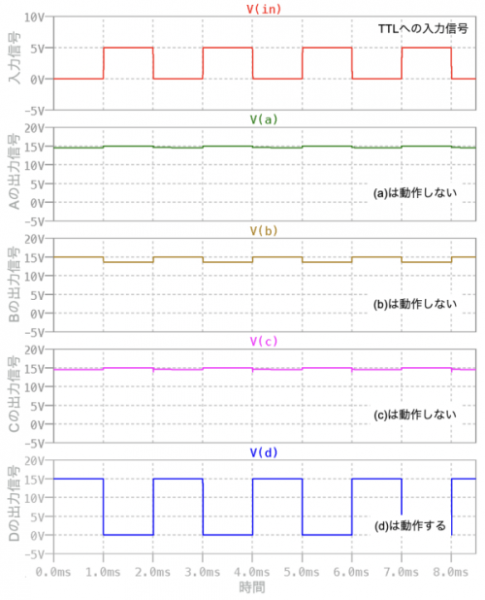

図4は,図1の回路に図2の4つのインターフェース回路を入れて,シミュレーションで動作を調べる回路です.シミュレーションはドット・コマンドの「.tran 8.5m」を指定し,0ms~8.5ms間のトランジェント解析を実行します.このトランジェント解析で,TTLインバータの入力信号が,CMOSインバータの各出力(A,B,C,D)に伝わるかを調べます.トランジスタのモデルパラメータは,「.include BJT_model.lib」のコマンドで読み込みます.

4種の回路について,問題の答え合わせをする.

図5は,図4のシミュレーション結果です.TTLインバータへの入力信号V(in),Aの回路の出力信号V(a),Bの回路の出力信号V(b),Cの回路の出力信号V(c),Dの回路の出力信号V(d) をプロットしました.先程の検討のように,Aの回路,Bの回路,Cの回路のインターフェースは15Vで動くCMOSの入力レベルの要件を満たさないので,動作していないことが分かります.一方,Dの回路のインターフェースはディジタル信号が伝わるので15Vのディジタル信号が現れ,動作していることが分かります.

このように,異なる電源で動作するTTLからCMOSへのインターフェースは,図2(d)のエミッタ接地回路を使い,負荷抵抗(RL)はCMOS側の電源に接続します.インターフェース回路で使うNPNトランジスタの耐圧は,CMOS側の電源以上のデバイスにします.このようにすることで,TTLの5Vのディジタル信号をインターフェース回路で15Vのディジタル信号に変換して,CMOSロジックの入力レベルに合わせています.

(a),(b),(c)は動作しない.(d)は動作する.

●異なる電源で動作するTTLからCMOSへのインターフェース(その2)

異なる電源で動作するTTLからCMOSへのインターフェースの2つ目の方法として,インターフェースにオープン・コレクタのTTLを使う方法があります.TTLロジック・ファミリの7407のようなオープン・コレクタのTTLは,出力端子にNPNトランジスタのコレクタが出ている出力形式で,外部で負荷を接続して信号を伝えます.オープン・コレクタのTTLは,TTLバッファとも呼ばれます.

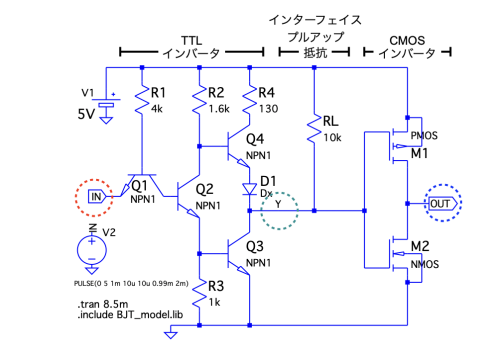

図6はインターフェースにオープン・コレクタのTTLを使った回路です.Q8のコレクタがオープン・コレクタ形式になり,負荷抵抗(RL)はCMOS側の電源に接続します.先程の図2(d)のエミッタ接地のトランジスタの代替としてオープンコレクタのTTLを用いる方法になります.

オープンコレクタのTTLを使う

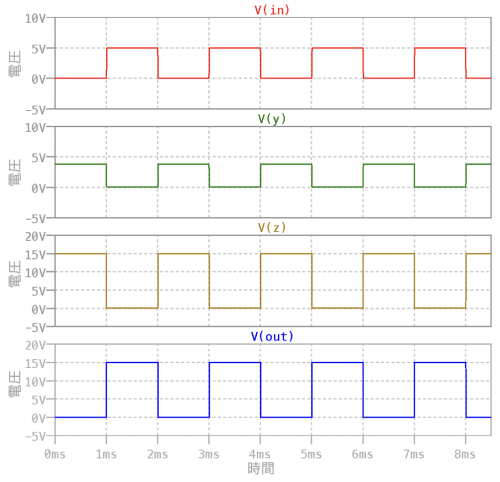

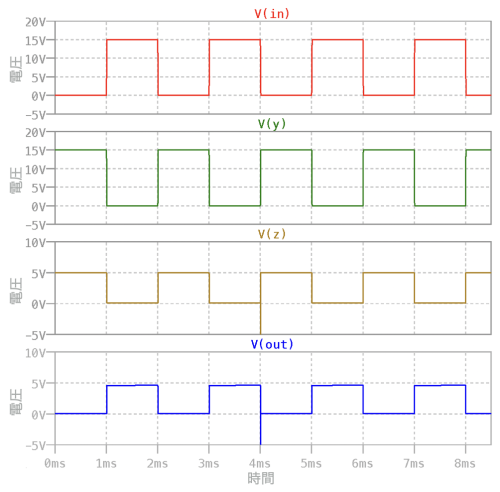

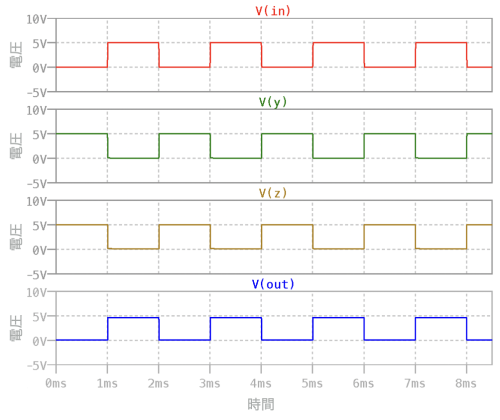

図7は,図6のシミュレーション結果です.TTLインバータへの入力信号V(in),TTLとインターフェース回路の接続点であるYの信号V(y),インターフェースとCMOSインバータの接続点であるZの信号V(z),CMOSインバータの出力信号V(out)をプロットしました.

入力信号V(in)は,TTLインバータを通り,5Vのディジタル信号V(y)になります.V(y)の信号は,インターフェース回路を通り,オープン・コレクタ端子にプルアップ抵抗を入れることにより,15Vのディジタル信号V(z)に変換されます.V(z)の信号はCMOSインバータの入力信号になるので,OUTには15Vのディジタル信号が現れます.

オープンコレクタとプルアップ抵抗により,TTL出力のVOHは電源までスイングする.

●同じ電源で動作するTTLからCMOSへのインターフェース

図8は,同じ電源で動作するTTLインバータとCMOSインバータを接続した回路になります.TTLとCMOSの間にあるプルアップ抵抗により,CMOSの入力レベルになるようにしています.具体的には,図8のプルアップ抵抗がないと,TTLの"H"側出力レベルの最小電圧は,図3(a)のように「VOH=2.4V」です.

電源とTTL出力間にプルアップ抵抗を入れる.

一方,CMOS側は電源が5Vのとき,図3(b)のように"H"側の入力レベルは「VIH≥3.3V」ですので,TTL側の出力レベルが低すぎます.このようなときはプルアップ抵抗を入れて,2つのインバータの接続点であるYの電圧を"H"のときに電源の5Vになるようにします.

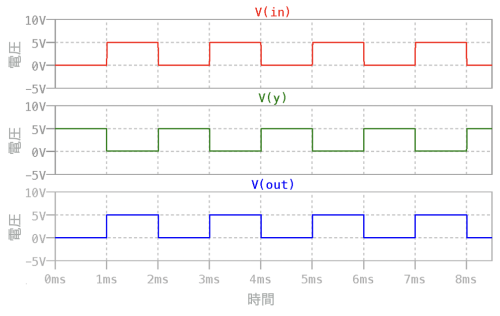

図9は,図8のシミュレーション結果です.TTLインバータへの入力信号V(in),TTLとCMOSの接続点であるYの信号V(y),CMOSインバータの出力信号V(out)をプロットしました.入力信号V(in)はTTLインバータを通り,プルアップ抵抗を入れることにより,V(y)は0V~5Vのディジタル信号になります.V(y)の信号はCMOSインバータの入力信号になるので,OUTには5Vのディジタル信号が現れます.

プルアップ抵抗により,接続点のYの信号は電源までスイングする.

●CMOSからTTLへのインターフェースについて

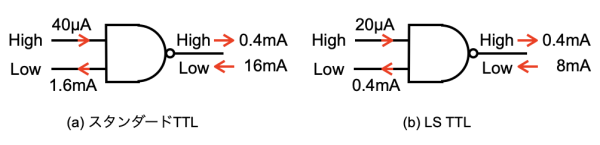

次にCMOSからTTLへのインターフェースを解説します.CMOSからTTLのインターフェースで気をつけることは,図2の入力レベルと出力レベルの他に,TTLの入力に流れる電流についても検討が必要です.図10にスタンダードTTL[図10(a)]とLS TTL[図10(b):低電力ショットキーTTL]の入力と出力に流れる電流を図示しました.図10(a)のスタンダードTTLを例にすると,入力が"H"のときには40μAの電流がTTL側に流れ,入力が"L"のときはTTL側から1.6mAが出てきます.CMOSの出力電流は,この2つの電流より大きな電流能力が必要になり,電流能力が小さいと"H"/"L"の論理を保てなくなります.

●異なる電源で動作するCMOSからTTLへのインターフェース

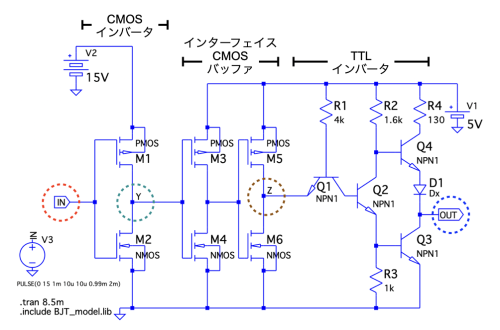

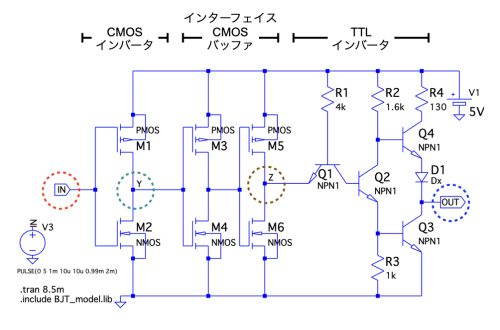

図11は,異なる電源で動作するCMOSインバータとTTLインバータを接続した回路になります.インターフェースは,CMOSバッファを用います.電源はTTLと同じ5Vに接続します.CMOSバッファの出力レベル(Zの電圧)は,図3(b)のように"H"のとき「VOH=5V-0.05V=4.95V」,"L"のとき「VOL=0.05V」になります.この出力レベルは,図3(a)のTTLの"H"の入力レベル「VIH≥2.0V」と"L"の入力レベル「VIL≤0.8V」を満たすので入力レベルに問題はありません.次に電流能力ですが,CMOSロジック・ファミリの4049UBのようなCMOSバッファは,TTLの入力電流より電流能力が高い設計になっており,TTLの入力電流を吸い込んだり,吐き出したりすることができます.

インターフェースにTTLの電源に接続したCMOSバッファを使う.

図12は,図11のシミュレーション結果です.CMOSインバータへの入力信号V(in),CMOSインバータとインターフェース回路の接続点であるYの信号V(y),インターフェースとTTLインバータの接続点であるZの信号V(z),TTLインバータの出力信号V(out)をプロットしました.入力信号V(in)は,CMOSインバータを通り,15Vのディジタル信号V(y)になります.V(y)の信号はインターフェース回路を通り,5Vのディジタル信号V(z)に変換されます.V(z)の信号はTTLインバータの入力信号になるので,OUTには5Vのディジタル信号が現れます.

●同じ電源で動作するCMOSからTTLへのインターフェース

図13は,同じ電源で動作するCMOSインバータとTTLインバータを接続した回路になります.インターフェースにはCMOSバッファを用います.先程の検討の通り,CMOSバッファの出力レベルとTTLの入力レベルは問題なく,CMOSバッファの出力電流能力も問題ありません.

インターフェースにCMOSバッファを使う.

図14は,図13のシミュレーション結果です.CMOSインバータへの入力信号V(in),CMOSインバータとインターフェース回路の接続点であるYの信号V(y),インターフェースとTTLインバータの接続点であるZの信号V(z),TTLインバータの出力信号V(out)をプロットしました.入力信号V(in)はCMOSインバータを通り,5Vのディジタル信号V(y)になります.V(y)の信号はインターフェース回路を通り,5Vのディジタル信号V(z)に変換されます.V(z)の信号はTTLインバータの入力信号になるので,OUTには5Vのディジタル信号が現れます.

以上,TTLとCMOSのインターフェースは入力レベルと出力レベルの違いを補完するインターフェースを使い,接続したときに"H"/"L"の論理を保つ電流条件を満たすことが必要です.TTLの内部回路と使用したモデルパラメータの詳細は,過去のメルマガ「TTLの論理ゲート」を参照してください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice7_042.zip

●データ・ファイル内容

TTL to CMOS2 Interface.asc:図4の回路

TTL to CMOS2 Interface.plt:図4のプロットを指定するファイル

TTL to CMOS3.asc:図6の回路

TTL to CMOS3 Interface.plt:図6のプロットを指定するファイル

TTL to CMOS1.asc:図8の回路

TTL to CMOS1.plt:図8のプロットを指定するファイル

CMOS to TTL2.asc:図11の回路

CMOS to TTL2.plt:図11のプロットを指定するファイル

CMOS to TTL1.asc:図13の回路

CMOS to TTL1.plt:図13のプロットを指定するファイル

BJT_model.lib:BJTのモデルファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) トランジスタ技術公式サイト LTspiceの部屋はこちら

(04) LTspice メール・マガジン全アーカイブs

(05) ◆LTspice電子回路マラソン・アーカイブs

(06) ◆LTspiceアナログ電子回路入門アーカイブs

(07) ◆LTspice電源&アナログ回路入門アーカイブs

(08) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(09) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(10) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs